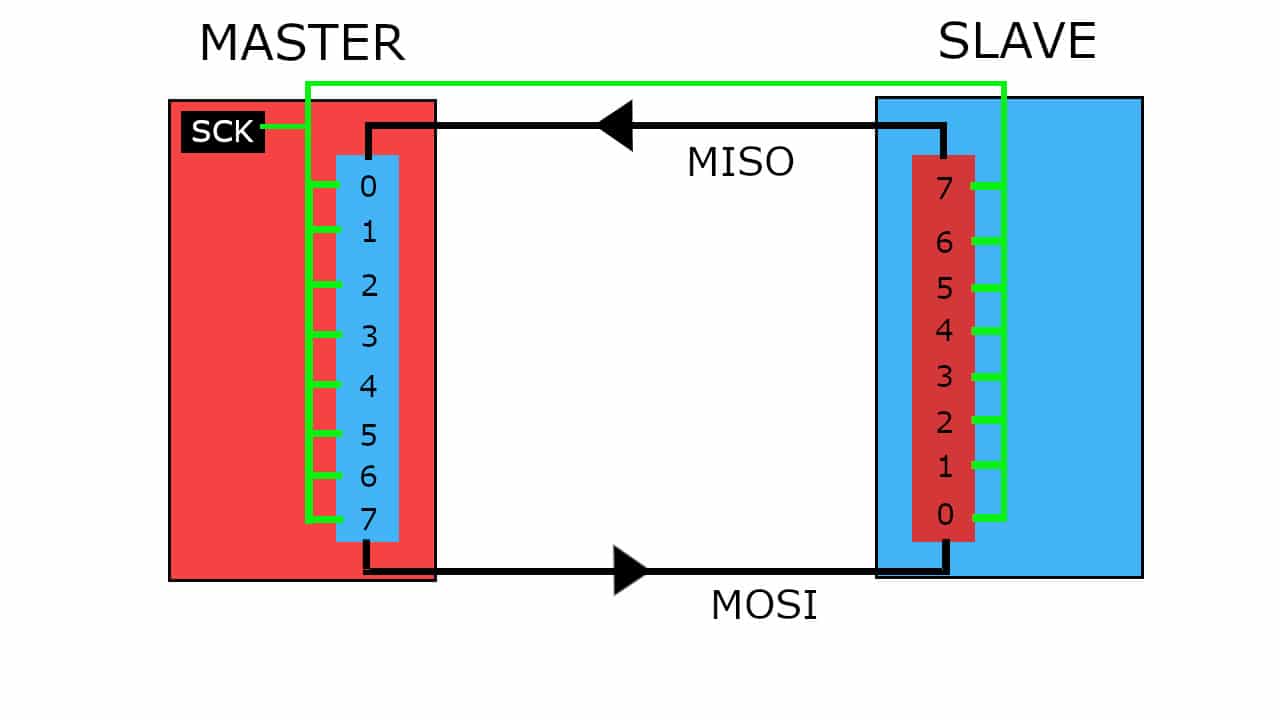

The SPI communication interface belongs to the full duplex interfaces, which means sending and receiving a signal at the same time. The SPI interface belongs to the family of synchronous interfaces, i.e. clock signal transmission, which allows synchronization of any system connected to the interface. The MASTER system is responsible for generating the SPI clock signal and starting the transmission of the signal. Other circuits connected to the same SPI interface take the form of SLAVE.

SPI standard

The construction of the SPI bus consists of four communication lines.

– MISO is Master in Slave out, means the line that connects the slave output to the master input,

– MOSI is Master out Slave in, a line that connects the master output with the slave input,

– SCK is a serial clock, a zero signal, it is designed to synchronize circuits,

– CS is chip select, a line informing slaves about the start of transmission, activation of slaves is performed using a high state, and deactivation by means of a low state, the signal is negated.

SPI principle of operation

The SPI interface is built on shift registers, which consist of type D flip-flops. The synchronization of each of them is performed by means of a clock signal. There are 8 flip-flops with numbers from 0 to 7. A logic state is entered at the input of flip-flop No. 0, which starts the transmission frame.

Each flip-flop stores one byte of data. The MASTER system generates a zero signal using a generator. The combined MOSI and MISO lines form a closed ring, thanks to which the data transfer is continuous but not constant, every eight clock cycles of the generator are sent the entire byte of data. The register value can be changed every 8 clock cycles.

SPI communication type

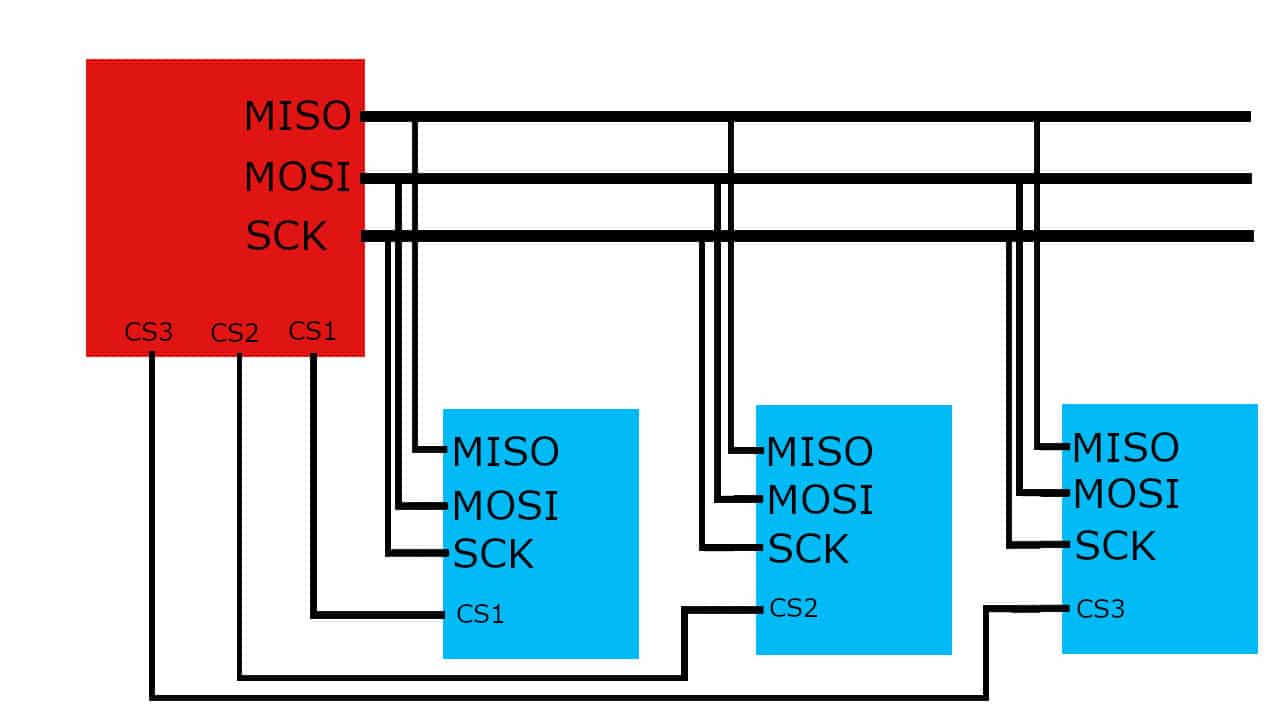

To read data from the SLAVE system, the system must send only zeros at the same time informing about its presence MASTER. There is a three-state buffer at the SLAVE output. When SLAVE is switched off by MASTER, the three-state buffer disconnects the shift register from the entire bus, thanks to which the SLAVE system cannot be seen through MASTER.

A typical type of SPI interface connection is a bus line connection. In this setting, MOSI, MISO and SCK lines are connected in parallel. Connection of the CS line is separate for each SLAVE. This is done in such a way as to activate each system individually.

SPI data frame

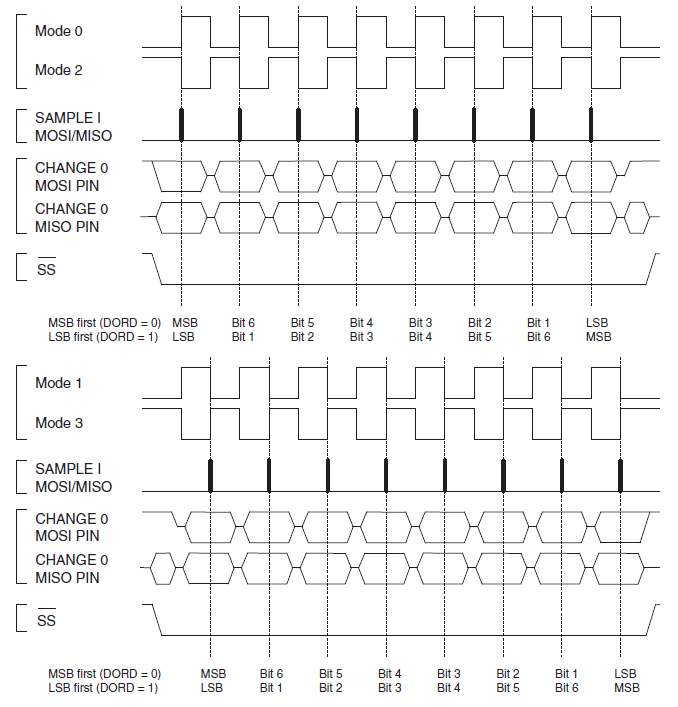

Sending data frame for SPI interface isn’t set by default. As bus users, we can determine whether frame sending will start from the oldest bit or the youngest bit. Data shifting in registers can also be set for the falling or rising edge of the SCK signal.

SPI Clock Polarity and SPI Clock Phase

The SPI idle state must match on the connected master and slave device. Additionally, the data clocking method during the transfer through the SPI interface must be the same.

Clock Polarity CPOL is an indicator that allows you to determine the level of the clock signal for the idle state.

CPOL 0 – Low status for idle state

CPOL 1 – High status for idle state

CPHA or the clock phase parameter determines the moment of sampling and presenting the data.

CPHA 0 – The first edge is responsible for sampling the signal of the first bit for the SCK line. The second edge is for the presentation function. The starting data bit must be prepared before transferring the first edge of the SCK line.

CPHA 1 – The first edge for the SCK line is used for data presentation. The second edge, on the other hand, is responsible for signal sampling.

The following schematic drawings show combinations for clock polarity settings and for clock phases.

Advantages and disadvantages of the SPI interface

Adventages:

- Full-duplex communication type

- Much faster data transfer compared to I2C interfaces

- Freedom to define the type of data transmission protocol (no restrictions for the maximum value of 8-bit, no addressing required)

- Very simple structure of spi hardware (emulation thanks to bit-banging, SLAVE connection allows for synchronization of transmission for SCLK signals)

- Parallel transmission requires few connections for spi hardware

Disadvantages:

- More occupied pins than in the I2C interfaces

- It has no hardware control for data flow

- No control bits between MASTER SLAVE devices

- The spi hardware system can have only one MASTER device

- Small maximum distance for data transmission

3 wire SPI connection example DS1868 with SPI microcontroller PIC16F872

An example component in this configuration is DS1868. It is a dual digital potentiometer connected via the 3 wire spi interface. The device that will manage the operation of the potentiometer is spi microcontroller with an active SPITM interface.

Normal SPI interface and 3 wire spi interface differ in signal types, but they are compatible. As for the 3 wire interface, the signals are DQ – signal with input data, Cout – main data, RST – switching signal, Active-Low – switching signal, CLK – clock signal.

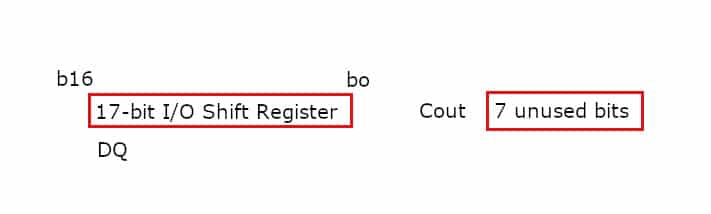

Data storage from the DS1868 potentiometer

Connecting the spi microcontroller to the DS1868 requires the MSB to be sent first. When writing data, the data frame contains 7 bits for the first byte which are pushed out of the shift register. The LSB for the first byte is in b0. The transfer data frame is 3 bytes long. This includes 17 data bits and 7 addressing and initialization bits.

Reading data from DS1868

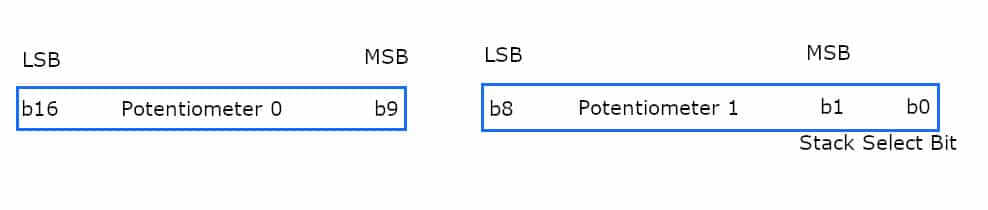

The transmit data frame for the DS1868 in 3 wire spi transmission looks as below in the figure. First, the stack select bit called b0 is sent, followed by the MSB of data from potentiometer # 1, then data from the next potentiometer. There are an additional 7 bits in the third data byte.

The flowchart for saving and reading data is presented below. The stack select bit is accommodated by byte 1, which is 0Fh. Byte 0 of the data frame has a value of 55h. The bytes to be written to the DS1868 device are those with the values 01h, 0Fh, 55h. The additional 7 bits are contained in the leading zeros 01h of the address. The SPI microcontroller first sends the MSB value, i.e. 01h. The leading zeros drop off and the value 1 ends at b0. In the first data frame, the first 4 bits are 0, the last 4 bits are filled with 1. The remaining bits change between 0 and 1. The value of the MSB bit in the pool for 0 is also 0.

- Byte 0: 00000001b (01h)

- Byte 1: 00001111b (0Fh)

- Byte 2: 01010101b (55h)

The 3 byte output values have the following values, and b0 is the first bit for reading.

- Byte 0: 10000111 (87h)

- Byte 1: 10101010 (AAh)

- Byte 2: 10,000,000 (80h)

The 7 additional bits are now at the end of byte 2.

The TRISx register establishes the pins to either input (1) or output (0 ). The PORTA register will certainly regulate the energetic reduced RST and the LED to 5V or 0V.

TRISA =– 1xxx00 – RA5 active-low SS is readied to input. It is used to make it possible for the serial port. RA0 and RA1 are readied to outputs for energetic low signal RST and also LED diode.

TRISB = lack of usage

TRISC = xx010xxx – Cleaning SCK i SDO, set SDI

The active-low RST pin should be set before sending out/ obtaining information and then must be removed after the sending data frame.

SPI settings

SSPSTAT = 01000000 (40h) – SMP bit = 0, CKE little bit = 1

When SMP = 0, the input data is tested at the end of the data exit time.

When CKE = 1, transmission occurs at the shift from the active clock state to the idle state when CKP = 0.

The SSPSTAT register establishes the clock and information to have the appropriate timing to link to the DS1868.

SSPCON = 00100001 (21h) – bit SSPEN = 1, bit SSPM3-0 = 0001

SSPEN = 1 enables the serial port.

SSPM3-0 has picked the clock regularity. SSPM3-0 = 0001 = Fosc/ 16 = 20 MHz/ 16 = 1.25 MHz

DS1868 has an optimum clock frequency of 10 MHz.

; ***************** ; App Note Code ; The following code was developed on the PIC16F872. ; ***************** LIST p=16F872 #INCLUDE GOTO MAIN ; ***Subroutines*** ; Delay for LED WAIT MOVWF 0x23 MOVLW 0x20 MOVWF 0x20 DEC1 DECFSZ 0x20 GOTO LOOP1 RETURN LOOP1 MOVLW 0xFF MOVWF 0X21 DEC2 DECFSZ 0X21 GOTO LOOP2 GOTO DEC1 LOOP2 MOVLW 0xFF MOVWF 0x22 DEC3 DECFSZ 0X22 GOTO DEC3 GOTO DEC2 ; ************************************* ; Test to Determine is TX is Complete DONE BSF STATUS, RP0 ; Select Bank 1 BTFSS SSPSTAT,0 ; Test SSPBUF to determine if TX is complete GOTO DONE RETURN ; ************************************** ; Initialize PORTA INITA BCF STATUS, RP0 ; Select Bank 0 BCF STATUS, RP1 CLRF PORTA ; Clear output data latches BSF STATUS, RP0 ; Select Bank 1 MOVLW 0x06 ; All outputs set digital MOVWF ADCON1 MOVLW 0x20 ; Value used to initialize data direction MOVWF TRISA ; LED and active-low RST outputs BCF STATUS, RP0 ; Select Bank 0 BCF STATUS, RP1 BSF PORTA, 1 ; LED off BCF PORTA, 0 ; active-low RST = 0V RETURN ; ************************************** ; Initialize PORTC INITC BCF STATUS, RP0 ; Select Bank 0 BCF STATUS, RP1 CLRF PORTC ; Clear output data latches BSF STATUS, RP0 ; Select Bank 1 MOVLW 0x10 ; Value used to initialize data direction MOVWF TRISC ; Clears SCK and SDO, sets SDI RETURN ; ************************************** ; Initialize SPI SPI BSF STATUS, RP0 ; Select Bank 1 MOVLW 0x40 MOVWF SSPSTAT ; SMP=0, CKE=1: These bits set up the data & clock. BCF STATUS, RP0 ; Select Bank 0 BCF STATUS, RP1 MOVLW 0x21 MOVWF SSPCON ; SSPEN=1, CKP=SSPMx=0001 (Fosc/16) RETURN ; *************************************** ; Initialize POT1 WRITE0 BCF STATUS, RP0 ; Select Bank 0 BCF STATUS, RP1 BSF PORTA, 0 ; active-low RST = 5V MOVLW 0x00 ; Clear Byte 0 MOVWF SSPBUF CALL DONE ; Test SSPBUF to determine if TX is complete BCF STATUS, RP0 ; Select Bank 0 BCF STATUS, RP1 MOVLW 0x00 ; Clear Byte 1 MOVWF SSPBUF CALL DONE ; Test SSPBUF to determine if TX is complete BCF STATUS, RP0 ; Select Bank 0 BCF STATUS, RP1 MOVLW 0x00 ; Clear Byte 2 MOVWF SSPBUF CALL DONE ; Test SSPBUF to determine if TX is complete BCF STATUS, RP0 ; Select Bank 0 BCF STATUS, RP1 BCF PORTA, 0 ; active-low RST = 0V RETURN ; *************************************** ; Write to Pot1 WRITE BCF STATUS, RP0 ; Select Bank 0 BCF STATUS, RP1 BSF PORTA, 0 ; active-low RST = 5V MOVLW 0x01 ; Stack Select bit = 1 (Byte 0) MOVWF SSPBUF CALL DONE BCF STATUS, RP0 ; Select Bank 0 BCF STATUS, RP1 MOVLW 0xFF ; Pot1 = FF (Byte 1) MOVWF SSPBUF CALL DONE BCF STATUS, RP0 ; Select Bank 0 BCF STATUS, RP1 MOVLW 0x80 ; Pot0 = 80 (Byte 2) MOVWF SSPBUF CALL DONE BCF STATUS, RP0 ; Bank0 BCF STATUS, RP1 BCF PORTA, 0 ; active-low RST = 0V RETURN ; *************************************** ; Compare Data Transmitted and Received CMPR BCF STATUS, RP ; Select Bank 0 BCF STATUS, RP1 BSF PORTA, 0 ; active-low RST = 5V MOVLW 0x01 ; Write Byte 0 MOVWF SSPBUF BCF PORTA, 1 ; LED on CALL DONE BCF STATUS, RP0 ; Select Bank 0 BCF STATUS, RP1 MOVF SSPBUF, 0 ; Read Byte 0 XORLW 0xFF BTFSS STATUS, 2 GOTO FAIL MOVLW 0xFF ; Write Byte 1 MOVWF SSPBUF CALL DONE BCF STATUS, RP0 ; Select Bank 0 BCF STATUS, RP1 MOVF SSPBUF, 0 ; Read Byte 1 XORLW 0xC0 BTFSS STATUS, 2 GOTO FAIL MOVLW 0x80 ; Write Byte 2 MOVWF SSPBUF CALL DONE BCF STATUS, RP0 ; Select Bank 0 BCF STATUS, RP1 MOVF SSPBUF, 0 ; Read Byte 2 ANDLW 0x80 BTFSS STATUS, 2 GOTO FAIL BCF PORTA, 0 ; active-low RST = 0V GOTO PASS RETURN ; *************************************** ; If Compare Fails FAIL BCF STATUS, RP0 ; Select Bank 0 BCF STATUS, RP1 CLRF PORTA ; Initialize PORTA by clearing output data latches BSF STATUS, RP0 ; Select Bank 1 MOVLW 0x06 ; All outputs set digital MOVWF ADCON1 MOVLW 0x20 ; Value used to initialize data direction MOVWF TRISA ; LED on and active-low RST high BCF STATUS, RP0 ; Select Bank 0 BCF STATUS, RP1 BCF PORTA, 1 ; LED on CALL WAIT BSF PORTA, 1 ; LED off CALL WAIT GOTO FAIL ; Repeat blinking LED ; *********************************** ; If Compare Passes PASS BCF STATUS, RP0 ; Select Bank 0 BCF STATUS, RP1 BCF PORTA, 1 ; LED on GOTO PASS ; LED remains on ; ******THE MAIN PROGRAM******** MAIN CALL INITA ; Initialize PORTA CALL INITC ; Initialize PORTC CALL SPI ; Initialize SPI CALL WRITE0 ; Initialize Pots CALL WRITE ; Write data to pots CALL CMPR Compare data written to pots w/ data received from pots END

[/vc_toggle]

Hardware implementation of SPI controller in CPLD

In the described example, the PPI subsystem is connected to the SPI transmitter, which was set in the slave operation mode. For a specific configuration, the master device in the system is Raspberry PI automation. The SCK clock transmits the signal frequency for the data and command bytes that are transmitted over the MOSI pin. The interruption data and data frame are transmitted by the MISO output pin. The /INT signal in the PPI subsystem serves as the interrupt operation.

The command decoder, which operates in a strobe combination circuit, is responsible for controlling the remaining blocks. The system operation mode depends on the S2-0 code. The RESET line signal activation is on during the reset mode for the strobe /STR signal. The addressing mode for the demultiplexer is responsible for configuring the CS3-0, A1 and A0 bits assigned to the address register which is responsible to control the 6-bit address bus. The data write mode for the demultiplexer causes the sending of a byte to the data bus driver, the /OC type signal, which is responsible for setting the byte for the bidirectional D7-0 bus, generating the write /WR signal for the specific chip and internal register 82C55A. The ability to transfer data to the Raspberry PI is achieved in the data read mode of the instruction decoder. The decoder sets the /RD signal, the multiplexer transfers the data for the SPI register in SPI controller configuration and the pulse /SP forces parallel write.

The /INT interruption handler reads and writes data for the Raspberry PI. Activating the /INT line, receiving INTR7-0 interrupts, which are reported by the 82C55A chips, and coding the priority call numbers, all these tasks are handled by a priority encoder. The answer to the encoder is to program the read mode for the interrupt number. The initialization of the transfer of the interrupt vector that comes from the multiplexer and the parallel entry to the SPI controller is controlled by the / STR signal. When serial reading for the contents of the SPI register, the Raspberry PI identifies a accomplished event that must be performed first.

It is really a nice and useful piece of info.

I am happy that you shared this helpful info with us.

Please keep us up to date like this. Thanks for sharing.

Does your site have a contact page? I’m having a tough time

locating it but, I’d like to send you an e-mail.

I’ve got some ideas for your blog you might be interested in hearing.

Either way, great blog and I look forward to seeing it grow over time.

I feel this is among the such a lot vital info

for me. And i am glad studying your article. However wanna statement on few basic things, The web site

taste is wonderful, the articles is actually great :

D. Just right process, cheers

Nice post. I was checking constantly this blog and I’m impressed!

Extremely useful info particularly the last part 🙂 I care for such information much.

I was seeking this particular info for a very long time.

Thank you and best of luck.

I got this site from my friend who told me concerning this site

and now this time I am browsing this web page and reading very informative posts

at this time.

Hello There. I discovered your weblog using msn. This is an extremely neatly written article.

I’ll make sure to bookmark it and come back to read more of your useful information. Thank you for the post.

I’ll definitely return.

Very nice post. I just stumbled upon your blog and wished

to say that I have really enjoyed browsing your blog posts.

After all I’ll be subscribing to your rss feed and I hope you write again soon!

Howdy! Do you use Twitter? I’d like to follow you

if that would be ok. I’m undoubtedly enjoying your blog

and look forward to new posts.

I think that what you composed made a bunch of sense.

However, what about this? suppose you were to write a awesome headline?

I mean, I don’t want to tell you how to run your

website, however suppose you added a headline to maybe get people’s attention? I mean SPI communication – How SPI works ?

is a little vanilla. You ought to peek at Yahoo’s front page and see how they create post titles to get viewers interested.

You might try adding a video or a related pic or two to get

readers excited about what you’ve got to say. Just my opinion, it would bring

your website a little livelier.

What’s up everyone, it’s my first pay a quick visit

at this web page, and article is in fact fruitful in support of me, keep up posting such articles

or reviews.

My brother suggested I might like this website. He was entirely right.

This post actually made my day. You cann’t imagine just how much time I had spent for this information! Thanks!

Wow that was odd. I just wrote an really long comment but after I clicked submit my comment didn’t show up.

Grrrr… well I’m not writing all that over again. Regardless, just wanted to say great blog!

Very nice post. I just stumbled upon yokur blog and wanted to say that I’ve truly enjoyed surfing arounnd your blog posts.

In any case I will be subscribing to you feed and I hope you wrte agazin very soon!